Post Doctoral Researcher

CMU, Pittsburgh, USA

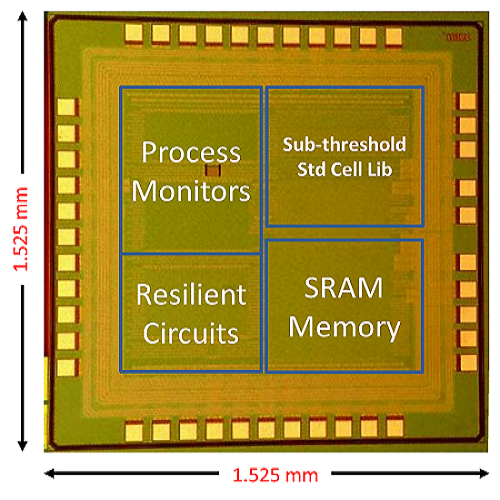

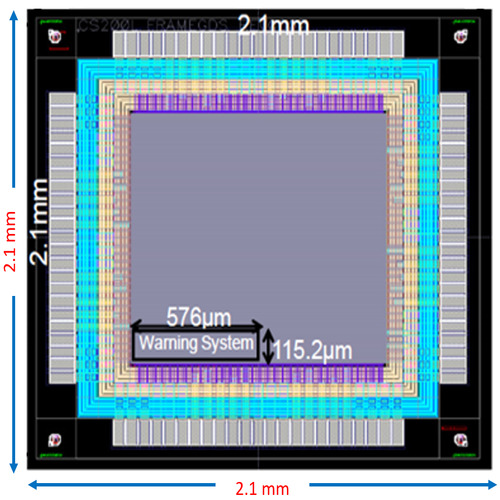

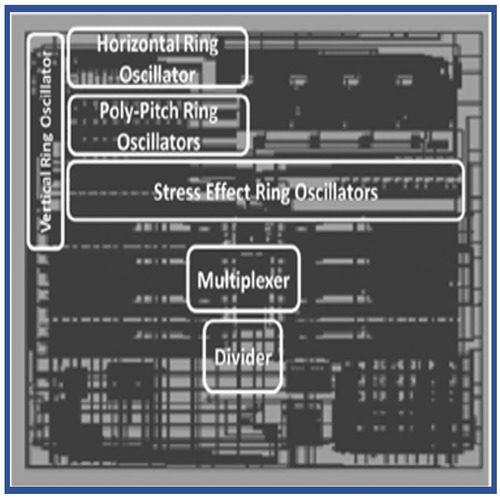

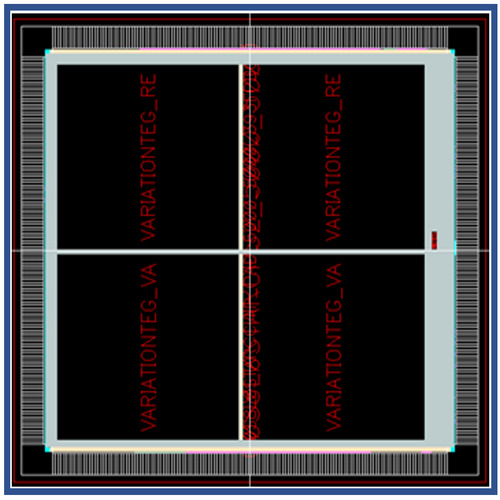

During July 2012 to Dec 2013, Prof. Das worked as a Post-Doctoral Researcher with the Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, USA, in the project entitled Trusted Integrated Circuit Design.